# Chip Errata for the i.MX 6Solo/6DualLite

This document details the silicon errata known at the time of publication for the i.MX 6Solo/6DualLite multimedia applications processors.

Table 1 provides a revision history for this document.

# **Table 1. Document Revision History**

| Rev.<br>Number | Date    | Substantive Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev. 6         | 08/2016 | Updated the following: ERR003717, ERR003718, ERR003719, ERR003720, ERR003721, ERR003723, ERR003724, ERR003725, ERR003726, ERR003726, ERR003727, ERR003728, ERR003739, ERR003731, ERR003732, ERR003733, ERR003733, ERR003734, ERR003735, ERR003736, ERR003737, ERR003738, ERR003739, ERR003741, ERR003743, ERR004324, ERR004326, ERR004327, ERR005175, ERR005183, ERR005185, ERR005187, ERR005198, ERR005200, ERR005382, ERR005383, ERR005385, ERR005386, ERR005387, ERR005391, ERR006259, ERR009605, ERR005766, ERR009219, ERR004446, ERR004512, ERR005783, ERR005895, ERR004573, ERR005992, ERR008000, ERR004341, ERR008000, ERR005828, ERR005829, ERR008001, ERR004307, ERR007805, ERR004366, ERR005172, ERR005190, ERR005191, ERR005192, ERR005193, ERR005194, ERR005195, ERR005196, ERR005197, ERR005191, ERR005192, ERR005193, ERR005194, ERR005195, ERR003753, ERR005197, ERR003755, ERR003756, ERR003747, ERR003749, ERR003751, ERR003753, ERR003754, ERR003755, ERR003756, ERR003757, ERR003758, ERR003759, ERR003759, ERR003759, ERR003759, ERR003754, ERR003755, ERR003756, ERR003757, ERR003754, ERR003759, ERR003759, ERR003759, ERR003759, ERR003759, ERR004297, ERR004298, ERR004299, ERR004321, ERR004374, ERR004489, ERR004490, ERR004491, ERR005186, ERR005188, ERR005189, ERR007554, ERR007559, ERR005645, ERR003778, ERR005764, ERR004534, ERR006281, ERR007122, ERR007220, ERR007266, ERR009678, ERR007117, ERR007006, ERR007007, ERR007008, ERR006887, ERR005829, ERR005908, ERR004325, ERR004484, ERR005216, ERR004535, ERR005723, ERR005852, ERR005566, ERR004325, ERR005778, ERR005895, ERR005313, ERR005991, ERR007926.  Added the folllowing: ERR009604, ERR009605, ERR009742, ERR009743, ERR009219, ERR009858, ERR009165, ERR009535, ERR009606, ERR009704, ERR009678, ERR009678, ERR008990, ERR007881, ERR005184. |

| Rev. 5         | 12/2014 | <ul> <li>Updated ERR008057</li> <li>Updated ERR005768</li> <li>Added ERR008506</li> <li>Added ERR007555</li> <li>Added ERR007556</li> <li>Added ERR007557</li> <li>Added ERR007559</li> <li>Added ERR007573</li> <li>Added ERR007575</li> <li>Added ERR007577</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Rev. 4         | 06/2014 | <ul> <li>Added ERR007805</li> <li>Added ERR008001</li> <li>Added ERR008057</li> <li>Added ERR007554</li> <li>Added ERR007926</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Rev. 3         | 11/2013 | <ul> <li>Updated Figure 1, "Revision Level to Part Marking Cross-Reference."</li> <li>Added the following: ERR007005, ERR007006, ERR007007, ERR007008, ERR007117, ERR007122, ERR007220, ERR007265, ERR007266</li> <li>Updated the following: ERR003778, ERR004512, ERR005313, ERR005991</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

**Table 1. Document Revision History (continued)**

| Rev.<br>Number | Date    | Substantive Changes                                                                                                                                                                                                               |

|----------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev. 2         | 5/2013  | <ul> <li>Deleted ERR004353</li> <li>Added the following errata: <ul> <li>ERR006308</li> <li>ERR006358</li> <li>ERR006687</li> </ul> </li> <li>Updated the following: <ul> <li>ERR004446</li> <li>ERR005829</li> </ul> </li> </ul> |

| Rev. 1.1       | 2/2013  | Restored pages omitted in Rev. 1.                                                                                                                                                                                                 |

| Rev. 1         | 1/2013  | Added the following:     ERR006223     ERR006259     ERR006281                                                                                                                                                                    |

| Rev. 0         | 10/2012 | Initial public release.                                                                                                                                                                                                           |

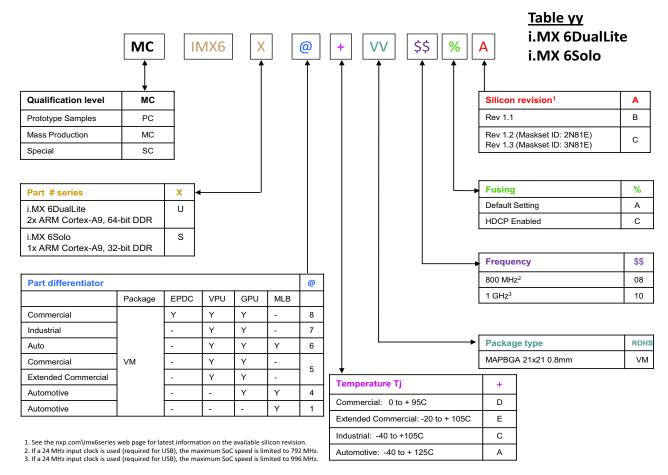

Figure 1 provides a cross-reference to match the revision code to the revision level marked on the device.

Figure 1. Revision Level to Part Marking Cross-Reference

Chip Errata for the i.MX 6Solo/6DualLite, Rev. 6

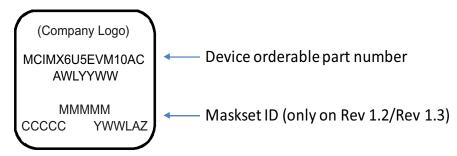

Figure 2 shows an example part marking for Revision 1.2/1.3 devices.

Figure 2. Example Part Marking for Revision 1.2/1.3 Devices

For details on the ARM® configuration used on this chip (including ARM module revisions), please see the "Platform configuration" section of the "ARM Cortex®-A9 MPCore Platform" chapter of the *i.MX 6Solo/6DualLite Applications Processor Reference Manual*.

# Table 2 summarizes errata on the i.MX 6Solo/6DualLite.

# Table 2. Summary of Silicon Errata

| Errata    | Name                                                                                                                               | Solution         | Page |  |

|-----------|------------------------------------------------------------------------------------------------------------------------------------|------------------|------|--|

|           | Analog                                                                                                                             |                  |      |  |

| ERR005852 | Analog: Transition from Deep Sleep Mode to LDO Bypass Mode may cause the slow response of the VDDARM_CAP output                    | No fix scheduled | 13   |  |

|           | ARM®                                                                                                                               | l                | •    |  |

| ERR003717 | ARM: 740657—Global Timer can send two interrupts for the same event                                                                | No fix scheduled | 14   |  |

| ERR003718 | ARM: 743622—Faulty logic in the Store Buffer may lead to data corruption                                                           | No fix scheduled | 16   |  |

| ERR003719 | ARM: 751469—Overflow in PMU counters may not be detected                                                                           | No fix scheduled | 18   |  |

| ERR003720 | ARM/MP: 751472—An interrupted ICIALLUIS operation may prevent the completion of a following broadcast operation                    | No fix scheduled | 20   |  |

| ERR003721 | ARM: 751473—Under very rare circumstances, Automatic Data prefetcher can lead to deadlock or data corruption                       | No fix scheduled | 22   |  |

| ERR003723 | ARM: 751476—May miss a watchpoint on the second part of an unaligned access that crosses a page boundary                           | No fix scheduled | 23   |  |

| ERR003724 | ARM: 754322—Possible faulty MMU translations following an ASID switch                                                              | No fix scheduled | 24   |  |

| ERR003725 | ARM: 725631—ISB is counted in Performance Monitor events 0x0C and 0x0D                                                             | No fix scheduled | 26   |  |

| ERR003726 | ARM: 729817—MainID register alias addresses are not mapped on Debug APB interface                                                  | No fix scheduled | 27   |  |

| ERR003727 | ARM: 729818—In debug state, next instruction is stalled when sdabort flag is set, instead of being discarded                       | No fix scheduled | 28   |  |

| ERR003728 | ARM: 740661—Event 0x74 / PMUEVENT[38:37] may be inaccurate                                                                         | No fix scheduled | 29   |  |

| ERR003729 | ARM: 740663—Event 0x68 / PMUEVENT[9:8] may be inaccurate                                                                           | No fix scheduled | 30   |  |

| ERR003730 | ARM: 743623—Bad interaction between a minimum of seven PLDs and one Non-Cacheable LDM can lead to a deadlock                       | No fix scheduled | 32   |  |

| ERR003731 | ARM: 743626—An imprecise external abort, received while the processor enters WFI, may cause a processor deadlock                   | No fix scheduled | 34   |  |

| ERR003732 | ARM: 751471—DBGPCSR format is incorrect                                                                                            | No fix scheduled | 35   |  |

| ERR003733 | ARM: 751480—Conditional failed LDREXcc can set the exclusive monitor                                                               | No fix scheduled | 37   |  |

| ERR003734 | ARM: 752519—An imprecise abort may be reported twice on non-cacheable reads                                                        | No fix scheduled | 38   |  |

| ERR003735 | ARM: 754323—Repeated Store in the same cache line may delay the visibility of the Store                                            | No fix scheduled | 39   |  |

| ERR003736 | ARM: 756421—Sticky Pipeline Advance bit cannot be cleared from debug APB accesses                                                  | No fix scheduled | 41   |  |

| ERR003737 | ARM: 757119—Some "Unallocated memory hint" instructions generate an UNDEFINED exception instead of being treated as NOP            | No fix scheduled | 42   |  |

| ERR003738 | ARM: 751475—Parity error may not be reported on full cache line access (eviction / coherent data transfer / cp15 clean operations) | No fix scheduled | 43   |  |

Table 2. Summary of Silicon Errata (continued)

| Errata    | Name                                                                                                                                                            | Solution         | Page |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------|

| ERR003739 | ARM: 751470—Imprecise abort on the last data of a cache linefill may not be detected                                                                            | No fix scheduled | 44   |

| ERR003741 | ARM/PL310: 729815—The "High Priority for SO and Dev reads" feature can cause Quality of Service issues to cacheable read transactions                           | No fix scheduled | 45   |

| ERR003743 | ARM/PL310: 754670—A continuous write flow can stall a read targeting the same memory area                                                                       | No fix scheduled | 46   |

| ERR004324 | ARM/MP: 761319—Ordering of read accesses to the same memory location may not be ensured                                                                         | No fix scheduled | 47   |

| ERR004325 | ARM/MP: 764369—Data or unified cache line maintenance operation by MVA may not succeed on an Inner Shareable memory region                                      | No fix scheduled | 48   |

| ERR004326 | ARM/MP: 761321—MRC and MCR are not counted in event 0x68                                                                                                        | No fix scheduled | 50   |

| ERR004327 | ARM/MP: 764319—Read accesses to DBGPRSR and DBGOSLSR may generate an unexpected UNDEF                                                                           | No fix scheduled | 51   |

| ERR005175 | ARM/MP: 771221—PLD instructions may allocate data in the Data Cache regardless of the Cache Enable bit value                                                    | No fix scheduled | 52   |

| ERR005183 | ARM/MP: 771224—Visibility of Debug Enable access rights to enable/disable tracing is not ensured by an ISB                                                      | No fix scheduled | 53   |

| ERR005185 | ARM/MP: 771225—Speculative cacheable reads to aborting memory region clear the internal exclusive monitor, may lead to livelock                                 | No fix scheduled | 54   |

| ERR005187 | ARM/MP: 771223—Parity errors on BTAC and GHB are reported on PARITYFAIL[7:6], regardless of the Parity Enable bit value                                         | No fix scheduled | 56   |

| ERR005198 | ARM/PL310: 780370—DATAERR, TAGERR, and Tag parity errors are incorrectly sampled by the eviction buffer, leading to data corruption                             | No fix scheduled | 57   |

| ERR005200 | ARM/MP: 765569—Prefetcher can cross 4 KB boundary if offset is programmed with value 23                                                                         | No fix scheduled | 60   |

| ERR005382 | ARM/MP: 775419—PMU event 0x0A (exception return) might count twice the LDM PC ^ instructions with base address register write-back                              | No fix scheduled | 61   |

| ERR005383 | ARM/MP: 775420—A data cache maintenance operation that aborts, followed by an ISB and without any DSB in-between, might lead to deadlock                        | No fix scheduled | 62   |

| ERR005385 | ARM/MP: 782772—A speculative execution of a Load-Exclusive or Store-Exclusive instruction after a write to Strongly Ordered memory might deadlock the processor | No fix scheduled | 63   |

| ERR005386 | ARM/MP: 782773—Updating a translation entry to move a page mapping might erroneously cause an unexpected translation fault                                      | No fix scheduled | 65   |

| ERR005387 | ARM/MP: 782774—A spurious event 0x63, "STREX passed," can be reported on an LDREX that is preceded by a write to Strongly Ordered memory region                 | No fix scheduled | 67   |

| ERR005391 | ARM: Debug CTI interrupt can cause a system deadlock when power gating the core                                                                                 | No fix scheduled | 68   |

| ERR006259 | ARM: Debug/trace functions (PMU, PTM and ETB) are disabled with absence of JTAG_TCK clock after POR                                                             | No fix scheduled | 69   |

| ERR007006 | ARM/MP:794072 Short loop including a DMB instruction might cause a denial of service                                                                            | No fix scheduled | 70   |

Table 2. Summary of Silicon Errata (continued)

| Errata    | Name                                                                                                                                             | Solution         | Page |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------|

| ERR007007 | ARM/MP: 794073 Speculative instruction fetches with MMU disabled might not comply with architectural requirements                                | No fix scheduled | 72   |

| ERR007008 | ARM/MP: 794074A write request to Uncacheable Shareable memory region might be executed twice                                                     | No fix scheduled | 73   |

| ERR009604 | ARM (CA9): 845369 — Under very rare timing circumstances, transition into streaming mode might create a data corruption                          | No fix scheduled | 75   |

| ERR009605 | ARM (CA9): 761320—Full cache line writes to the same memory                                                                                      | No fix scheduled | 77   |

| ERR009742 | ARM: 795769 - "Write Context ID" event is updated on read access                                                                                 | No fix scheduled | 79   |

| ERR009743 | ARM: 799770 - DBGPRSR Sticky Reset status bit is set to 1 by the CPU debug reset instead of by the CPU non-debug reset                           | No fix scheduled | 80   |

| ERR009858 | ARM/PL310: 796171 When data banking is implemented, data parity errors can be incorrectly generated                                              | No fix scheduled | 81   |

|           | CAAM                                                                                                                                             |                  | 1    |

| ERR005766 | CAAM: CAAM cannot handle interleaved READ data "beats" returned by two different slaves in the system, in reply to two different AXI-ID accesses | No fix scheduled | 82   |

|           | ССМ                                                                                                                                              |                  | 1    |

| ERR006223 | CCM: Failure to resume from Wait/Stop mode with power gating                                                                                     | No fix scheduled | 83   |

| ERR007265 | CCM: When improper low-power sequence is used, the SoC enters low power mode before the ARM core executes WFI                                    | No fix scheduled | 84   |

| ERR009219 | CCM: Asynchronous clock switching can cause unpredictable behavior                                                                               | No fix scheduled | 85   |

|           | eCSPI                                                                                                                                            |                  | 1    |

| ERR009165 | eCSPI: TXFIFO empty flag glitch can cause the current FIFO transfer to be sent twice                                                             | No fix scheduled | 87   |

| ERR009535 | eCSPI: Burst completion by SS signal in slave mode is not functional                                                                             | No fix scheduled | 88   |

| ERR009606 | eCSPI: In master mode, burst lengths of 32n+1 will transmit incorrect data                                                                       | No fix scheduled | 89   |

|           | EIM                                                                                                                                              |                  | •    |

| ERR004446 | EIM: AUS mode is nonfunctional for devices larger than 32 MB                                                                                     | No fix scheduled | 90   |

|           | ENET                                                                                                                                             |                  | •    |

| ERR004512 | ENET: 1 Gb Ethernet MAC (ENET) system limitation                                                                                                 | No fix scheduled | 91   |

| ERR005783 | ENET: ENET Status FIFO may overflow due to consecutive short frames                                                                              | No fix scheduled | 92   |

| ERR005895 | ENET: ENET 1588 channel 2 event capture mode not functional                                                                                      | No fix scheduled | 93   |

| ERR006358 | ENET: Write to Transmit Descriptor Active Register (ENET_TDAR) is ignored                                                                        | No fix scheduled | 94   |

| ERR006687 | ENET: Only the ENET wake-up interrupt request can wake the system from Wait mode.                                                                | No fix scheduled | 95   |

|           | EPDC                                                                                                                                             | 1                |      |

|           |                                                                                                                                                  |                  |      |

Table 2. Summary of Silicon Errata (continued)

| Errata    | Name                                                                                                                                                                       | Solution         | Page |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------|

| ERR005313 | EPDC: Incorrect data fetched when the buffer update width is 2048 pixels or greater                                                                                        | No fix scheduled | 97   |

| ERR005991 | EPDC: Memory access may lock up when two continuous unaligned burst accesses return data back to back                                                                      | No fix scheduled | 98   |

| ERR005992 | EPDC: EPDC may not detect collision correctly on update buffer boundary when using >16 LUTs AND with unaligned update buffer AND have different LUT updating adjacent area | No fix scheduled | 99   |

|           | ESAI                                                                                                                                                                       |                  |      |

| ERR008000 | ESAI: ESAI may encounter channel swap when overrun/underrun occurs                                                                                                         | No fix scheduled | 100  |

|           | EXSC                                                                                                                                                                       |                  |      |

| ERR005828 | EXSC: Protecting the EIM memory map region causes unpredictable behavior                                                                                                   | No fix scheduled | 101  |

|           | FlexCAN                                                                                                                                                                    |                  | •    |

| ERR005829 | FlexCAN: FlexCAN does not transmit a message that is enabled to be transmitted in a specific moment during the arbitration process                                         | No fix scheduled | 102  |

|           | GРMI                                                                                                                                                                       |                  | •    |

| ERR008001 | GPMI: GPMI does not support the Set Feature command in Toggle mode                                                                                                         | No fix scheduled | 104  |

|           | GPU                                                                                                                                                                        |                  |      |

| ERR004300 | GPU3D: L1 cache performance drop                                                                                                                                           | No fix scheduled | 105  |

| ERR004341 | GPU2D: Accessing GPU2D when it is power-gated will cause a deadlock in the system                                                                                          | No fix scheduled | 106  |

| ERR004484 | GPU3D: L1 cache "Write Address Data" pairing error                                                                                                                         | No fix scheduled | 107  |

| ERR005216 | GPU3D: Black texels in Android App Singularity 3D                                                                                                                          | No fix scheduled | 108  |

| ERR005908 | GPU2D: Image quality degradation observed for stretch blits when the stretch factor is exactly an integer                                                                  | No fix scheduled | 109  |

|           | НДМІ                                                                                                                                                                       |                  |      |

| ERR004366 | HDMI: 9000482480—ARM core read operation returns incorrect data                                                                                                            | No fix scheduled | 110  |

| ERR005172 | HDMI: Under certain circumstances, the HDCP may transmit incorrect Ainfo value, causing a failure on the receiver side                                                     | No fix scheduled | 111  |

|           | I/O                                                                                                                                                                        |                  | •    |

| ERR004307 | I/O: MIPI_HSI, USB_HSIC, and ENET I/O interfaces should not be configured to Differential input mode                                                                       | No Fix scheduled | 112  |

|           | I2C                                                                                                                                                                        |                  | •    |

| ERR007805 | I2C: When ERR004307 I2C clock speed is configured for 400 kHz, the SCL low period violates the I2C specification                                                           | No fix scheduled | 113  |

Table 2. Summary of Silicon Errata (continued)

| Errata    | Name                                                                                                                                                                                                             | Solution                       | Page |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------|

|           | MIPI                                                                                                                                                                                                             |                                | 1    |

| ERR005190 | MIPI: CSI2 Data lanes are activated before the HS clock from the CSI Tx side (camera) starts                                                                                                                     | No fix scheduled               | 114  |

| ERR005191 | MIPI: Corruption of short command packets with Word Count (WC) greater than 16'hFFEE, during video mode transmission by the MIPI Generic Interface                                                               | No fix scheduled               | 115  |

| ERR005192 | MIPI: Reverse direction long packets with no payload incorrectly issue a CRC error for MIPI DSI                                                                                                                  | No fix scheduled               | 116  |

| ERR005193 | MIPI: The bits for setting the MIPI DSI video mode cannot be changed on the fly                                                                                                                                  | No fix scheduled               | 117  |

| ERR005194 | MIPI: On MIPI DSI, there is a possible corruption of the video packets caused by overlapping of the current line over the next line, if the configuration is programmed incorrectly when using the DPI interface | No fix scheduled               | 118  |

| ERR005195 | MIPI: Incorrect blanking packet may be sent by the MIPI DSI interface                                                                                                                                            | No fix scheduled               | 119  |

| ERR005196 | MIPI: Error Interrupt generated by the MIPI CSI interface for certain legal packet types                                                                                                                         | No fix scheduled               | 120  |

| ERR005197 | MIPI: Null and Blanking data packets activate 'dvalid' signal                                                                                                                                                    | No fix scheduled               | 121  |

| ERR009704 | MIPI: CSI-2: CRC error produced in 4-lane configuration                                                                                                                                                          | No fix scheduled               | 122  |

|           | MMDC                                                                                                                                                                                                             |                                |      |

| ERR005778 | MMDC: DDR Controller's measure unit may return an incorrect value when operating below 100 MHz                                                                                                                   | No fix scheduled               | 123  |

| ERR008057 | MMDC: Skew difference of up to 150 ps observed on SDCLK0, DQS0 and DQS7 differential traces                                                                                                                      | Fixed in silicon revision 1.3. | 124  |

| ERR009596 | MMDC: ARCR_GUARD bits of MMDC Core AXI Re-ordering Control register (MMDC_MAARCR) doesn't behave as expected                                                                                                     | No fix scheduled               | 125  |

|           | PCIe                                                                                                                                                                                                             |                                |      |

| ERR003747 | PCIe: 9000436491—Reading the Segmented Buffer Depth Port Logic registers returns all zeros                                                                                                                       | No fix scheduled               | 126  |

| ERR003748 | PCIe: 9000427578—Root ports with address translation drop inbound requests, without reporting an error                                                                                                           | No fix scheduled               | 127  |

| ERR003749 | PCIe: 9000426180—MSI Interrupt Controller Status Register bit not cleared after being written by software                                                                                                        | No fix scheduled               | 128  |

| ERR003751 | PCIe: 9000413207—PME Requester ID overwritten when two PMEs are received consecutively                                                                                                                           | No fix scheduled               | 129  |

| ERR003753 | PCIe: 9000405932—AXI/AHB Bridge Slave does not return a response to an outbound non-posted request                                                                                                               | No fix scheduled               | 130  |

| ERR003754 | PCIe: 9000403702—AHB/AXI Bridge Master responds with UR status instead of CA status for inbound MRd requesting greater than CX_REMOTE_RD_REQ_SIZE                                                                | No fix scheduled               | 131  |

| ERR003755 | PCIe: 9000402443—Uncorrectable Internal Error Severity register bit has incorrect default value                                                                                                                  | No fix scheduled               | 132  |

Table 2. Summary of Silicon Errata (continued)

| Errata    | Name                                                                                                                                                 | Solution          | Page |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------|

| ERR003756 | PCIe: 9000387484—LTSSM: Software-initiated transitions to Disabled, Hot Reset, Configuration, or Loopback states sometimes take longer than expected | No fix scheduled  | 133  |

| ERR003757 | PCIe: 9000448152—Internal Address Translation Unit (iATU): Inbound Vendor Defined Message (VDM) 'ID Match Mode' is not functional                    | No fix scheduled  | 134  |

| ERR003758 | PCIe: 9000441819—Upstream Port does not transition to Recovery after receiving TS OSs during "ENTER_L2 negotiation"                                  | No fix scheduled  | 135  |

| ERR003759 | PCIe: 9000439510—Internal Address Translation Unit (iATU) can sometimes overwrite Outbound (Tx) Vendor Messages and MSIs                             | No fix scheduled  | 136  |

| ERR003760 | PCIe: 9000439175—Poisoned Atomic Op requests targeting RTRGT0 receive UR response instead of CA response                                             | No fix scheduled  | 137  |

| ERR004297 | PCIe: 9000336356—Link configuration sometimes proceeds when incorrect TS Ordered Sets are received                                                   | No fix scheduled  | 138  |

| ERR004298 | PCIe: 900043—Bad DLLP error status checking is too strict                                                                                            | No fix scheduled  | 139  |

| ERR004299 | PCIe: 9000493959—L1 ASPM incorrectly entered after link down event during L1 ASPM entry negotiation                                                  | No fix scheduled  | 140  |

| ERR004321 | PCIe: 9000470913—Power Management Control: Core might enter L0s/L1 before Retry buffer is empty                                                      | No fix scheduled  | 141  |

| ERR004374 | PCIe: 9000487440—TLP sometimes unnecessarily replayed                                                                                                | No fix scheduled  | 143  |

| ERR004489 | PCIe: 9000505660—PCIe2 receiver equalizer settings                                                                                                   | No fix scheduled  | 144  |

| ERR004490 | PCIe: 9000514662—LTSSM delay when moving from L0 to recovery upon receipt of insufficient TS1 Ordered Sets                                           | No fix scheduled  | 145  |

| ERR004491 | PCIe: 9000507633—TLP might be replayed an extra time before core enters recovery                                                                     | No fix scheduled  | 147  |

| ERR005186 | PCIe: The PCIe Controller Core Does Not Send Enough TS2 Ordered Sets During Link Retrain And Speed Change                                            | No fix scheduled  | 149  |

| ERR005188 | PCIe: The PCIe Controller cannot exit successfully L1 state of LTSSM when the Core Clock is removed                                                  | No fix scheduled  | 150  |

| ERR005189 | PCIe: PCIe Gen2/Gen3 Hardware Autonomous Speed Disable Bit In Configuration Register is not sticky                                                   | No fix scheduled  | 151  |

| ERR005723 | PCIe: PCIe does not support L2 power down                                                                                                            | No fix scheduled  | 152  |

| ERR007554 | PCIe: MSI Mask Register Reserved Bits not read-only                                                                                                  | No fix scheduled. | 153  |

| ERR007555 | PCIe: iATU—Optional programmable CFG Shift feature for ECAM is not correctly updating address (9000642041)                                           | No fix scheduled  | 154  |

| ERR007556 | PCIe: Core Delays Transition From L0 To Recovery After Receiving Two TS OS And Erroneous Data                                                        | No fix scheduled  | 155  |

| ERR007557 | PCIe: Extra FTS sent when Extended Synch bit is set                                                                                                  | No fix scheduled  | 156  |

| ERR007559 | PCIe: Core sends TS1 with non-PAD lane number too early in Configuration.Linkwidth.Accept State                                                      | No fix scheduled  | 157  |

| ERR007573 | PCIe: Link and lane number-match not checked in recovery                                                                                             | No fix scheduled  | 158  |

Table 2. Summary of Silicon Errata (continued)

| Errata    | Name                                                                                                              | Solution                                                  | Page |

|-----------|-------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|------|

| ERR007575 | PCIe: LTSSM delay when moving from L0 to recovery upon receipt of insufficient TS1 Ordered Sets                   | No fix scheduled                                          | 159  |

| ERR007577 | PCIe: DLLP/TLP can be missed on RX path when immediately followed by EIOS                                         | No fix scheduled                                          | 160  |

|           | ROM                                                                                                               |                                                           | •    |

| ERR005645 | ROM: Normal SD clock speed (SDR12) not selectable in SD/SDXC boot mode                                            | No fix scheduled                                          | 161  |

| ERR005768 | ROM: In rare cases, secondary image boot flow may not work due to mis-sampling of the WDOG reset                  | Fixed in silicon revision 1.3.                            | 162  |

| ERR007117 | ROM: When booting from NAND flash, enfc_clk_root clock is not gated off when doing the clock source switch        | Fixed in i.MX<br>6Solo/6DualLite<br>silicon revision 1.2. | 163  |

| ERR007122 | ROM: TZASC_ENABLE fuse bit is coded in ROM as bit 24 at location 0x460 whereas the fuse map defines it as bit 28. | Fixed in i.MX<br>6Solo/6DualLite<br>silicon revision 1.2. | 165  |

| ERR007220 | ROM: NAND boot may fail due to incorrect Hamming checking implementation in the ROM code                          | Fixed in i.MX<br>6Solo/6DualLite<br>silicon revision 1.2. | 166  |

| ERR007266 | ROM: EIM NOR boot may fail if plug-in is used                                                                     | No fix scheduled                                          | 167  |

| ERR007926 | ROM: 32 kHz internal oscillator timing inaccuracy may affect SD/MMC, NAND, and OneNAND boot                       | Fixed in silicon revision 1.3                             | 168  |

| ERR008506 | ROM: Incorrect NAND BAD Block Management                                                                          | Fixed in silicon revision 1.3                             | 170  |

| ERR009678 | ROM: SD/EMMC/NAND prematurely times out during boot                                                               | No fix scheduled                                          | 171  |

|           | SSI                                                                                                               |                                                           | •    |

| ERR003778 | SSI: In AC97, 16-bit mode, received data is shifted by 4-bit locations                                            | No fix scheduled                                          | 172  |

| ERR005764 | SSI: AC97 receive data may be wrong when clock ratio between external clock to ipg is higher than 1:8             | No fix scheduled                                          | 173  |

| ERR008990 | SSI: Channel swap in single FIFO mode when an underrun or overrun occurs                                          | No fix scheduled                                          | 174  |

|           | USB                                                                                                               |                                                           |      |

| ERR004534 | USB: Wrong HS disconnection may be generated after resume                                                         | No fix scheduled                                          | 175  |

| ERR004535 | USB: USB suspend and resume flow clarifications                                                                   | No fix scheduled                                          | 176  |

| ERR006281 | USB: Incorrect DP/DN state when only VBUS is applied                                                              | No fix scheduled                                          | 177  |

| ERR006308 | USB: Host non-doubleword –aligned buffer address can cause host to hang on OUT Retry                              | No fix scheduled                                          | 178  |

| ERR007881 | USB: Timeout error in Device mode                                                                                 | No fix scheduled                                          | 179  |

|           | VPU                                                                                                               |                                                           |      |

| ERR004349 | VPU: Cannot decode Sorenson Spark Version 0 bitstream                                                             | No fix scheduled                                          | 180  |

# Table 2. Summary of Silicon Errata (continued)

| Errata    | Name                                                                             | Solution         | Page |  |

|-----------|----------------------------------------------------------------------------------|------------------|------|--|

| XTAL      |                                                                                  |                  |      |  |

| ERR005777 | XTAL: In some cases, the 24 MHz oscillator start-up is slow or may fail to start | No fix scheduled | 181  |  |

# ERR005852 Analog: Transition from Deep Sleep Mode to LDO Bypass Mode may cause the slow response of the VDDARM\_CAP output

# **Description:**

Normally, the VDDARM\_CAP supply takes only approximately 40 µs to raise to the correct voltage when exiting from Deep Sleep (DSM) mode, if the LDO is enabled. If the LDO bypass mode is selected, the VDDARM\_CAP supply voltage will drop to approximately 0 V when entering and when exiting from DSM, even though the VDDARM\_IN supply is already stable, the VDDARM CAP supply will take about 2 ms to rise to the correct voltage.

# **Projected Impact:**

ARM core might fail to resume.

#### Workarounds:

The software workaround to prevent this issue it to switch to analog bypass mode (0x1E), prior to entering DSM, and then, revert to the normal bypass mode, when exiting from DSM.

# **Proposed Solution:**

No fix scheduled

#### **Linux BSP Status:**

Software workaround implemented in Linux BSP codebase starting in release L3.0.35\_4.1.0.

# ERR003717 ARM: 740657—Global Timer can send two interrupts for the same event

# **Description:**

The Global Timer can be programmed to generate an interrupt request to the processor when it reaches a given programmed value. Due to the erratum, when the Global Timer is programmed not to use the auto-increment feature, it might generate two interrupt requests instead of one.

#### **Conditions:**

The Global Timer Control register is programmed with the following settings:

- Bit[3] = 1'b0 Global Timer is programmed in "single-shot" mode

- Bit[2] = 1'b1 Global Timer IRQ generation is enabled

- Bit[1] = 1'b1 Global Timer value comparison with Comparator registers is enabled

- Bit[0] = 1'b1 Global Timer count is enabled

With these settings, an IRQ is generated to the processor when the Global Timer value reaches the value programmed in the Comparator registers.

The Interrupt Handler then performs the following sequence:

- 1. Read the ICCIAR (Interrupt Acknowledge) register

- 2. Clear the Global Timer flag

- 3. Modify the comparator value to set it to a higher value

- 4. Write the ICCEOIR (End of Interrupt) register

Under these conditions, due to the erratum, the Global Timer might generate a second (spurious) interrupt request to the processor at the end of this Interrupt Handler sequence.

#### **Projected Impact:**

The erratum creates spurious interrupt requests in the system.

#### Workarounds:

Because the erratum only happens when the Global Timer is programmed in "single-shot" mode, that is, when it does not use the auto-increment feature, a first possible workaround could be to program the Global Timer to use the auto-increment feature.

If this solution does not work, a second workaround could be to modify the Interrupt Handler to avoid the offending sequence. This is achieved by clearing the Global Timer flag after having incremented the Comparator register value.

Then, the correct code sequence for the Interrupt Handler should look as below:

- 1. Read the ICCIAR (Interrupt Acknowledge) register

- 2. Modify the comparator value to set it to a higher value

- 3. Clear the Global Timer flag

- 4. Clear the Pending Status information for Interrupt 27 (Global Timer interrupt) in the Distributor of the Interrupt Controller.

Chip Errata for the i.MX 6Solo/6DualLite, Rev. 6

5. Write the ICCEOIR (End of Interrupt) register

# **Proposed Solution:**

No fix scheduled

#### **Linux BSP Status:**

Software workaround not implemented in the BSP. Functionality or mode of operation in which the erratum may manifest itself is not used. The BSP does not use ARM global timer. The configuration and logic of the kernel does not make use of the Global Timer. If the Global timer is used, the workaround documented by ARM should be followed. Due to limitations of this timer specifically in low power mode operation we do not recommend the use of this ARM Global timer.

# ERR003718 ARM: 743622—Faulty logic in the Store Buffer may lead to data corruption

# **Description:**

Under very rare conditions, a faulty optimization in the Cortex®-A9 store buffer might lead to data corruption.

#### Conditions:

The code sequence which exhibits the failure requires at least five cacheable writes in 64-bit data chunk:

- Three of the writes must be in the same cache line

- Another write must be in a different cache line

- All of the above four writes hit in the L1 data cache

- A fifth write is required in any of the above two cache lines that fully writes a 64-bit data chunk

With the above code sequence, under very rare circumstances, this fifth write might get corrupted, with the written data either being lost, or being written in another cache line.

The conditions under which the erratum can occur are extremely rare, and require the coincidence of multiple events and states in the Cortex-A9 micro-architecture.

As an example: let's assume A, A', A'', and A''' are all in the same cache line—B and B' are in another cache line. The following code sequence might trigger the erratum:

```

STR A

STR A'

STR A''

STR B

STR A''' (or STR B')

```

At the time where the first four STR are in the Cortex-A9 store buffer, and the fifth STR arrives at a very precise cycle in the Store Buffer input stage, then the fifth STR might not see its cache line dependency on the previous STR instructions. Because of this, in cases when the cache line A or B gets invalidated due to a coherent request from another CPU, the fifth STR might write in a faulty cache line, causing data corruption.

An alternative version of the erratum might happen even without a coherent request — In the case when the fifth STR is a 64-bit write in the same location as one of A, A', A'', then the erratum might also be exhibited. Note that this is a quite uncommon scenario because it requires a first write to a memory location that is immediately and fully overwritten.

# **Projected Impact:**

When it occurs, this erratum creates a data corruption.

#### Workarounds:

A software workaround is available for this erratum that requires setting bit[6] in the undocumented Diagnostic Control register, placed in CP15 c15 0 c0 1.

The bit can be written in Secure state only, with the following Read/Modify/Write code sequence:

Chip Errata for the i.MX 6Solo/6DualLite, Rev. 6

```

MRC p15,0,rt,c15,c0,1

ORR rt,rt,#0x40

MCR p15,0,rt,c15,c0,1

```

When this bit is set, the "fast lookup" optimization in the Store Buffer is disabled, which will prevent the failure to happen.

Setting this bit has no visible impact on the overall performance or power consumption of the processor.

# **Proposed Solution:**

No fix scheduled

#### **Linux BSP Status:**

Software workaround implemented in Linux BSP codebase (UBOOT) starting in release L3.0.35\_4.1.0.

#### ERR003719 ARM: 751469—Overflow in PMU counters may not be detected

#### **Description:**

Overflow detection logic in the Performance Monitor Counters is faulty, and under certain timing conditions, the overflow may remain undetected. In this case, the Overflow Flag Status register (PMOVSR) is not updated as it should, and no interrupt is reported on the corresponding PMUIRQ line.

It is important to notice that the Cycle counter is not affected by this erratum.

# **Projected Impact:**

PMU overflow detection is not reliable.

#### Workarounds:

The main workaround for this erratum is to poll the performance counter. The maximum increment in a single cycle for a given event is 2. Therefore, polling can be infrequent as no counter can increment by more than 2^32 in fewer than 2 billion cycles.

If the main usage model for performance counters is collecting values over a long period, then polling can be used to collect values (and reset the counter) rather than waiting for an overflow to occur. Polling can be done infrequently and overflow avoided.

If the main usage model for performance counters relies on presetting the counter to some value and waiting for an overflow to occur, then polling can be used to detect when an overflow event has been missed. An overflow can be determined to have been missed if the unsigned value in the counter is less than the value preset into the counter. Again, polling can be done infrequently because of the number of cycles it would need for this check to fail. In the case that the erratum was triggered and an overflow event was missed, that counter sample can be thrown away or the true value can be reconstructed.

An alternative workaround is to configure two counters to be triggered by the same event, staggering their initial count values by 1. This will result in the rollover being triggered by at least counter.

This alternative workaround works for all Cortex-A9 events but the three following ones, due to the fact these three events can increment by 2 in a single cycle:

- 0x68 Instructions coming out of the core renaming stage

- 0x73 Floating-point instructions

- 0x74 NEON instructions

For these 3 events, only the first workaround is applicable to fix the defect.

# **Proposed Solution:**

No fix scheduled

#### **Linux BSP Status:**

Software workaround is not implemented because this erratum will not be encountered in normal device operation. The Linux BSP does not support this optional profiling feature. Users may add support for this profiling feature as required, but should ensure the multiple errata impacting the ARM PMU are considered especially for multi-core usage.

#### ERR003720

# ARM/MP: 751472—An interrupted ICIALLUIS operation may prevent the completion of a following broadcast operation

# **Description:**

In an MPCore configuration with two or more processors working in SMP mode with maintenance operation broadcast enabled, if a processor is interrupted while executing an ICIALLUIS operation, and performs another broadcast maintenance operation during its Interrupt Service Routine, then this second operation might not be executed on other processors in the cluster.

#### Conditions:

The erratum requires an MPCore configuration with two or more CPUs working in SMP mode. One processor has interrupts enabled, and Cache and TLB maintenance broadcast enabled too (ACTLR.FW=1'b1). This processor executes an ICIALLUIS (invalidates all instruction caches Inner Shareable to Point of Unification). This instruction is executed on the processor, and also broadcast to other processors in the MPCore cluster. The processor then receives an interrupt (IRQ or FIQ), which interrupts the ICIALLUIS operation.

During the Interrupt Service Routine, the processor executes any other Cache or TLB maintenance operation which is also broadcast to other processors in the MPCore cluster. If the other processors in the cluster receive this second maintenance operation before having completed the first ICIALLUIS operation, then the erratum occurs, as the other processors will not execute the second maintenance operation. This is because there is no "stacking" mechanism for acknowledge answers between the processors, so that the acknowledge request sent to signify the completion of the ICIALLUIS will be interpreted by the originating processor as an acknowledge for the second maintenance operation.

# **Projected Impact:**

Due to the erratum, the processor might end up with corrupted entries in the Cache or in the TLB, leading to possible failures in the system.

#### Workarounds:

A software workaround is available for this erratum that involves setting bit[11] in the undocumented Diagnostic Control register, placed in CP15 c15 0 c0 1.

This bit can be written in Secure state only, with the following Read/Modify/Write code sequence:

```

MRC p15,0,rt,c15,c0,1

ORR rt,rt,#0x800

MCR p15,0,rt,c15,c0,1

```

When it is set, this bit prevents CP15 maintenance operations to be interrupted.

Using this software workaround is not expected to cause any visible impact on the system.

# **Proposed Solution:**

No fix scheduled

# **Linux BSP Status:**

Software workaround implemented in Linux BSP codebase (UBOOT) starting in release  $L3.0.35\_4.1.0$ .

# ERR003721 ARM: 751473—Under very rare circumstances, Automatic Data prefetcher can lead to deadlock or data corruption

# **Description:**

Under very rare timing circumstances, the automatic Data prefetcher might cause address hazard issues, possibly leading to a data corruption or a deadlock of the processor.

#### Conditions:

The erratum can only happen when the Data Cache and MMU are enabled in the following cases:

- On all memory regions marked as Write-Back Non-Shared, when the Data Prefetcher in L1 is enabled (ACTLR[2]=1'b1), regardless of the ACTLR.SMP bit.

- On all memory regions marked as Write-Back Shared, when the Data Prefetch Hint in L2 is enabled (ACTLR[1]=1'b1), and when the processor is in SMP mode (ACTLR.SMP=1'b1).

#### **Projected Impact:**

When the bug happens, a data corruption or a processor deadlock can happen.

#### Workarounds:

The workaround for this erratum requires not enabling the automatic Data Prefetcher by keeping ACTRL[2:1]=2'b00, which is the default value on exit from reset.

Although this feature might show significant performance gain on a few synthetic benchmarks, it usually has no impact on real systems. It means, this workaround is not expected to cause any visible impact on final products.

# **Proposed Solution:**

No fix scheduled

#### **Linux BSP Status:**

Software workaround not implemented in the BSP. Functionality or mode of operation in which the erratum may manifest itself is not used. Linux BSP keeps ACTRL[2:1]=2'b00.

# ERR003723 ARM: 751476—May miss a watchpoint on the second part of an unaligned access that crosses a page boundary

# **Description:**

Under rare conditions, a watchpoint on the second part of an unaligned access that crosses a 4 KB page boundary and that is missed in the micro-TLB for the second part of its request might be undetected.

The erratum requires a previous conditional instruction that accesses the second 4 KB memory region (= where the watchpoint is set), is missed in the micro-TLB, and is condition failed. The erratum also requires that no other micro-TLB miss occurs between this conditional failed instruction and the unaligned access. This implies that the unaligned access must hit in the micro-TLB for the first part of its request.

# **Projected Impact:**

A valid watchpoint trigger is missed.

#### Workarounds:

In case, a watchpoint is set on any of the first 3 bytes of a 4 KB memory region, and unaligned accesses are not being faulted, then the erratum might happen.

The workaround then requires setting a guard watchpoint on the last byte of the previous page, and dealing with any "false positive" matches as and when they occur.

# **Proposed Solution:**

No fix scheduled

#### **Linux BSP Status:**

A software workaround is not implemented because this erratum will not be encountered in normal device operation. The Linux BSP does not use this debug feature—the ARM workaround should be followed.

# ERR003724 ARM: 754322—Possible faulty MMU translations following an ASID switch

#### **Description:**

A microTLB entry might be corrupted following an ASID switch, possibly corrupting subsequent MMU translations.

The erratum requires execution of an explicit memory access, which might be speculative. This memory access misses in the TLB and cause a translation table walk. The erratum occurs when the translation table walk starts before the ASID switch code sequence, but completes after the ASID switch code sequence. In this case, a new entry is allocated in the microTLB for the TLB entry for this translation table walk, but corresponding to the old ASID. Because the microTLB does not record the ASID value, the new MMU translation, which should happen with the new ASID following the ASID switch, might hit this stale microTLB entry and become corrupted. Note that there is no Trustzone Security risk because the Security state of the access is held in the microTLB, and cannot be corrupted.

# **Projected Impact:**

The errata might cause MMU translation corruptions.

#### Workarounds:

The workaround for this erratum involves adding a DSB in the ASID switch code sequence. The ARM architecture only mandates ISB before and after the ASID switch. Adding a DSB prior to the ASID switch ensures that the Page Table Walk completes prior to the ASID change, so that no stale entry can be allocated in the micro-TLB.

The examples in the ARM Architecture Reference Manual for synchronizing the change in the ASID and TTBR need to be changed as follows:

The sequence:

```

Change ASID to 0

ISB

Change Translation Table Base Register

ISB

Change ASID to new value

becomes

DSB

Change ASID to 0

ISB

Change Translation Table Base Register

ISB

DSB

Change ASID to new value

the sequence:

Change Translation Table Base Register to the global-only mappings

```

Chip Errata for the i.MX 6Solo/6DualLite, Rev. 6

```

ISB

Change ASID to new value

Change Translation Table Base Register to new value

becomes

Change Translation Table Base Register to the global-only mappings

ISB

DSB

Change ASID to new value

Change Translation Table Base Register to new value

and the sequence:

Set TTBCR.PD0 = 1

ISB

Change ASID to new value

Change Translation Table Base Register to new value

Set TTBCR.PD0 = 0

becomes

Set TTBCR.PD0 = 1

ISB

DSB

Change ASID to new value

Change Translation Table Base Register to new value

Set TTBCR.PD0 = 0

```

# **Proposed Solution:**

No fix scheduled

#### **Linux BSP Status:**

Software workaround implemented in Linux BSP codebase starting in release L3.0.35 4.1.0.

ERR003725

# ERR003725 ARM: 725631—ISB is counted in Performance Monitor events 0x0C and 0x0D

# **Description:**

The ISB is implemented as a branch in the Cortex-A9 micro-architecture. This implies that events 0x0C (software change of PC) and 0x0D (immediate branch) are asserted when an ISB occurs. This is not compliant with the ARM architecture.

#### **Projected Impact:**

The count of events 0x0C and 0x0D are not 100% precise when using the Performance Monitor counters, due to the ISB being counted in addition to the real software changes to PC (for 0x0C) and immediate branches (0x0D).

The erratum also causes the corresponding PMUEVENT bits to toggle in case an ISB is executed.

- PMUEVENT[13] relates to event 0x0C

- PMUEVENT[14] relates to event 0x0D

#### Workarounds:

Count ISB instructions along with event 0x90. The user should subtract this ISB count from the results obtained in events 0x0C and 0x0D, to obtain the precise count of software change of PC (0x0C) and immediate branches (0x0D).

# **Proposed Solution:**

No fix scheduled

#### **Linux BSP Status:**

Software workaround is not implemented because this erratum will not be encountered in normal device operation. The Linux BSP does not support this optional profiling feature. Users may add support for this profiling feature as required, but should ensure the multiple errata impacting the ARM PMU are considered especially for multi-core usage.

# ERR003726 ARM: 729817—MainID register alias addresses are not mapped on Debug APB interface

# **Description:**

The ARM Debug Architecture specifies registers 838 and 839 as "Alias of the MainID register". They should be accessible through the APB Debug interface at addresses 0xD18 and 0xD1C. In Cortex-A9, the two alias addresses are not implemented. A read access at any of these two addresses returns 0, instead of the MIDR value.

Note that read accesses to these two registers through the internal CP14 interface are trapped to UNDEF, which is compliant with the ARM Debug architecture. So, the erratum only applies to the alias addresses through the external Debug APB interface.

# **Projected Impact:**

If the debugger or any other external agent tries to read the MIDR register using the alias addresses, it will get a faulty answer (0x0), which can cause all sorts of malfunction in the debugger afterwards.

#### Workarounds:

The workaround for this erratum requires always accessing the MIDR at its original address, 0xD00, and not at any of its alias addresses.

# **Proposed Solution:**

No fix scheduled

#### **Linux BSP Status:**

Software workaround is not implemented because this erratum will not be encountered in normal device operation.

ERR003727

# ERR003727 ARM: 729818—In debug state, next instruction is stalled when sdabort flag is set, instead of being discarded

# **Description:**

When the processor is in debug state, an instruction written to the ITR after a Load/Store instruction that aborts gets executed on clearing the SDABORT 1, instead of being discarded.

# **Projected Impact:**

Different failures can happen due to the instruction being executed when it should not. In most cases, it is expected that the failure will not cause any significant problem.

#### Workarounds:

There are a selection of workarounds with increasing complexity and decreasing impact. In each case, the impact is a loss of performance when debugging:

- Do not use stall mode

- Do not use stall mode when doing load/store operations

- Always check for a sticky abort after issuing a load/store operation in stall mode (the cost of this probably means the above second workaround is a preferred alternative)

- Always check for a sticky abort after issuing a load/store operation in stall mode, before issuing any further instructions that might corrupt important target state (such as, further load/store instructions, instructions that write to "live" registers [VFP, CP15, etc.])

# **Proposed Solution:**

No fix scheduled

#### **Linux BSP Status:**

Software workaround is not implemented because this erratum will not be encountered in normal device operation.

#### ERR003728 ARM: 740661—Event 0x74 / PMUEVENT[38:37] may be inaccurate

#### **Description:**

Event 0x74 counts the total number of Neon instructions passing through the register rename pipeline stage. Due to the erratum, the "stall" information is not taken into account. So, one Neon instruction that remains for n cycles in the register rename stage is counted as n Neon instructions. As a consequence, the count of event 0x74 might be corrupted, and cannot be relied upon. The event is also reported externally on PMUEVENT[38:37], which suffers from the same inaccuracy.

# **Projected Impact:**

The implication of this erratum is that Neon instructions cannot be counted reliably in the versions of the product that are affected by this erratum.

#### Workarounds:

No workaround is possible to achieve the required functionality of counting how many Neon instructions are executed (or renamed) in the processor.

# **Proposed Solution:**

No fix scheduled

#### **Linux BSP Status:**

Software workaround is not implemented because this erratum will not be encountered in normal device operation. The Linux BSP does not support this optional profiling feature. Users may add support for this profiling feature as required, but should ensure the multiple errata impacting the ARM PMU (Performance Monitoring Unit) are considered especially for multi-core usage.

#### ERR003729 ARM: 740663—Event 0x68 / PMUEVENT[9:8] may be inaccurate

#### **Description:**

Event 0x68 counts the total number of instructions passing through the register rename pipeline stage. Under certain conditions, some branch-related instructions might pass through this pipeline stage without being counted. As a consequence, event 0x68 might be inaccurate, lower than expected. The event is also reported externally on PMUEVENT[9:8], which suffers from the same inaccuracy.

#### Conditions:

The erratum occurs when the following conditions are met:

- Events are enabled

- One of the PMU counters is programmed to count event 0x68 number of instructions passing through the register rename stage. Alternatively, an external component counts, or relies on, PMUEVENT[9:8].

- A program, containing the following instructions, is executed:

- A Branch immediate, without Link

- An ISB instruction

- An HB instruction, without Link and without parameter, in Thumb2EE state

- An ENTERX or LEAVEX instruction, in Thumb2 or Thumb2EE state

- The program executed is causing some stalls in the processor pipeline

Under certain timing conditions specific to the Cortex-A9 micro-architecture, a cycle stall in the processor pipeline might "hide" the instructions mentioned above, thus ending with a corrupted count for event 0x68, or a corrupted value on PMUEVENT[9:8] during this given cycle. If the "hidden" instruction appears in a loop, the count difference can be significant.

As an example, let's consider the following loop:

```

loop mcr 15, 0, r2, cr9, cr12, {4}

adds r3, #1

cmp.w r3, #loop_number

bne.n loop

```

The loop contains four instructions; so, the final instruction count should (approximately) be four times the number of executed loops. In practice, the MCR is causing a pipeline stall that "hides" the branch instruction (bne.n); so, only three instructions are counted per loop, and the final count appears as three times the number of executed loops.

# **Projected Impact:**

The implication of this erratum is that the values of event 0x68 and PMUEVENT[9:8] are imprecise, and cannot be relied upon.

#### Workarounds:

No workaround is possible to achieve the required functionality of counting how many instructions are precisely passing through the register rename pipeline stage.

Chip Errata for the i.MX 6Solo/6DualLite, Rev. 6

31

# **Proposed Solution:**

No fix scheduled

## **Linux BSP Status:**

Software workaround is not implemented because this erratum will never be encountered in normal device operation. The Linux BSP does not support this optional profiling feature. Users may add support for this profiling feature as required, but should ensure the multiple errata impacting the ARM PMU (Performance Monitoring Unit) are considered especially for multi-core usage.

#### ERR003730

# ARM: 743623—Bad interaction between a minimum of seven PLDs and one Non-Cacheable LDM can lead to a deadlock

# **Description:**

Under very rare circumstances, a deadlock can happen in the processor when it is handling a minimum of seven PLD instructions, shortly followed by one LDM to an uncacheable memory location.

The LDM is treated as uncacheable in the following cases:

- The LDM is performed while the Data Cache is OFF

- The LDM is targeting a memory region marked as Strongly Ordered, Device, Normal Memory Non-Cacheable, or Normal Memory Write-Through